# ECE 8863 CR Lab Logistics

## Where

- Room 5148, 5<sup>th</sup> floor, Centergy One building, Tech Square

# When

- During your scheduled time slots or by appointment with a TA

## How

- Call BWN Lab (404) 894-6616 from 5<sup>th</sup> floor lobby

- Go to Room 5158 (BWN Lab) to sign in

- Do your Lab work (TAs are available in Room 5158)

- Show deliverables to TAs

- Sign out

#### IFA'2013

### ECE8863

# In the Lab

## CR Testbed Hardware

- USRP N210 x 5

- Wideband RF frontend

- Dell host laptops

- GB Ethernet switch

- CR Testbed Software

- GNU Radio SDR platform

- Ubuntu OS

- Universal Hardware Driver (UHD)

- Internet access: GTwpa

- No wired Internet access IFA'2013 ECE886

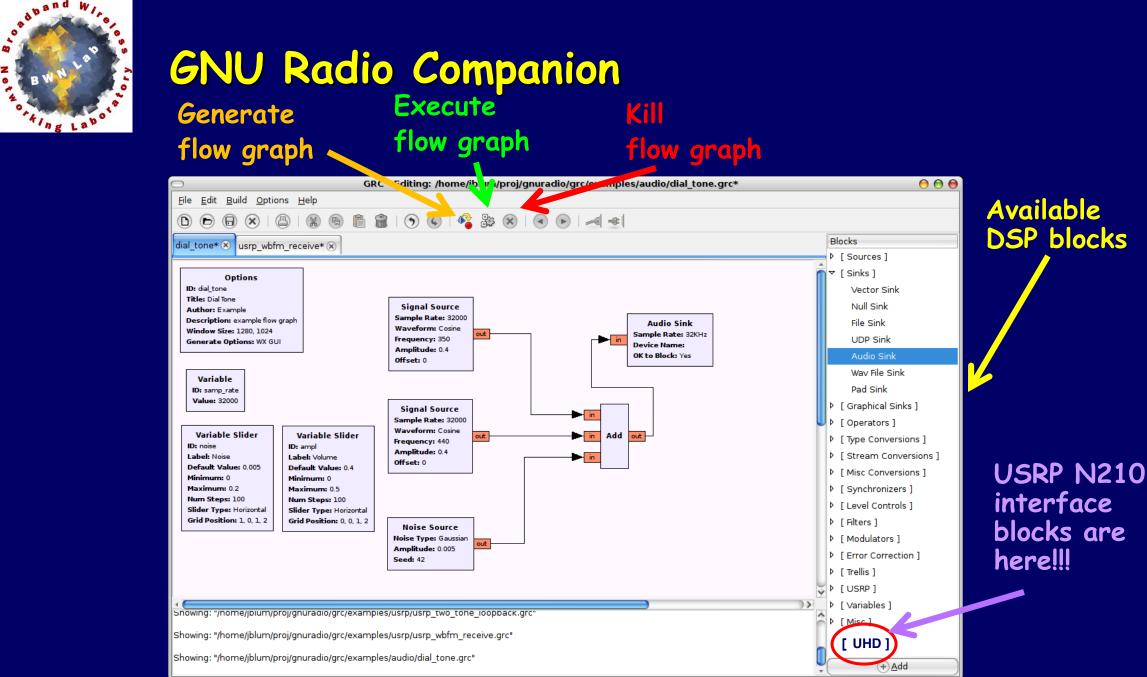

## Meet the Software

# GNU Radio

- Free software development toolkit (in Python and C++)

- Provide signal processing runtime and processing blocks to implement software radios

- Use readily available, low cost external RF hardware and commodity processors

- Graphical user interface: gnuradio-companion (used to be grc)

## Universal Hardware Driver (UHD)

- UHD provides a host driver and API for USRPs

#### IFA'2013

#### ECE8863

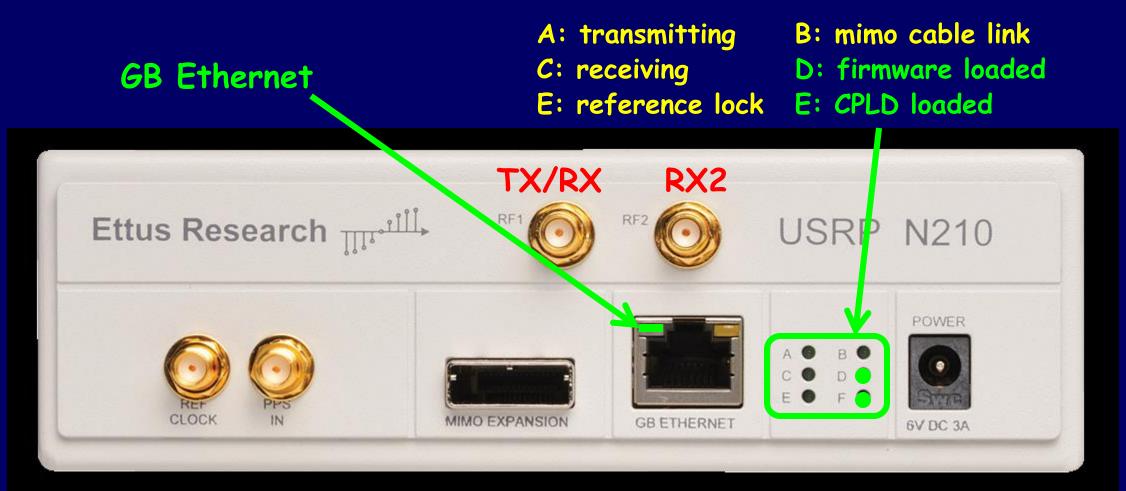

# USRP N210 Front View

## Working state: verify these 3 green lights

**ECE8863**

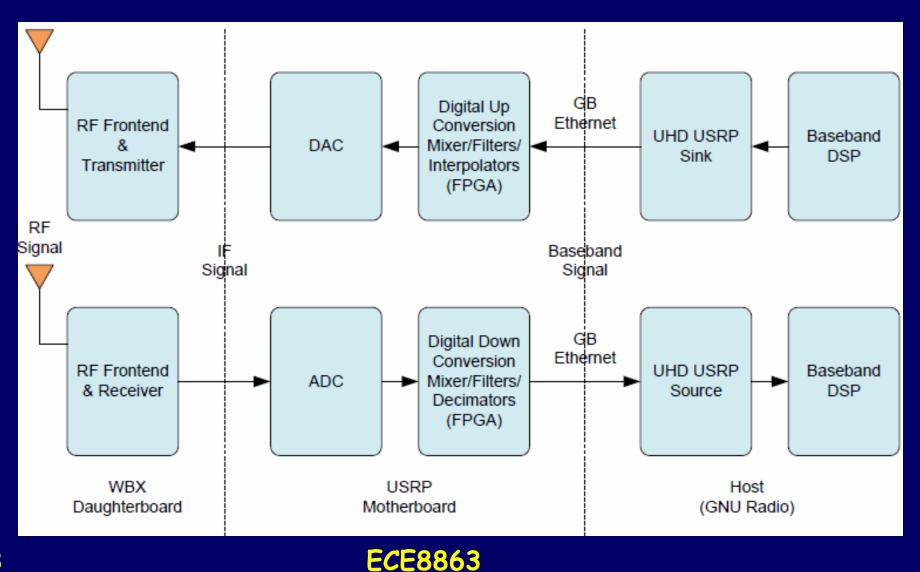

# **CR** Testbed Block Diagram

# and W/.

# Universal Software Radio Peripheral (USRP)

## Latest Version of USRP N210 Motherboard

- 2 channels or 1 I-Q pair for both input and output

- Dual 100 MHz 14-bit ADCs

- Dual 400 MHz 16-bit DACs

- 50/25 MHz instantaneous RF bandwidth (8/16-bit mode)

- Processing/Streaming signals up to 100MHz/50MHz wide

- Xilinx Spartan 3A-DSP3400 FPGA (with 32-bit RISC processor)

- 1 MB of high-speed SRAM

- Configuration and firmware stored in onboard Flash

- External ref clock: 5/10 MHz and 1 PPS (pulse per second) input

- Gigabit Ethernet interface

- MIMO expansion capability

#### IFA'2013

#### ECE8863

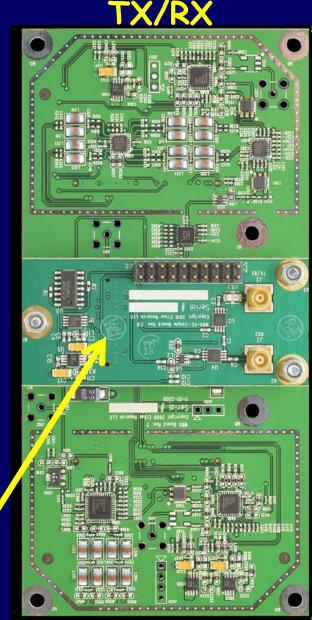

# **WBX Transceiver Daughterboard**

### 50MHz-2.2GHz Full-duplex Transceiver

- Transmit antenna: TX/RX

- Receive antenna: TX/RX or RX2

- When using WBX in full-duplex mode, the receive antenna will always be set to RX2

- Transmit gain range: 0-25 dB

- Receive gain range: 0-31.5 dB

- Bandwidth: RX: 40 MHz and TX: 40 MHz

- Cover white spaces, broadcast TV and FM radio, public safety radio, land mobile, WSNs, cell phones, and 6 amateur radio bands

**ECE8863**

LNA/filter board

# Antennas: VERT400 and VERT900

## VERT400 (COMET SMA703)

- 144 MHz, 430 MHz, 1200 MHz Tri-band

- 118-160, 250-290, 360-390, 420-470, 820-960

MHz bands

- Gain: 3.4dBi (1200MHz)

- 7-inch vertical antenna

### **VERT900**

824-960 MHz, 1710-1990 MHz Quad-band

Cellular/PCS and ISM band

**ECE8863**

- Gain: 3dBi Gain

- 9-inch vertical antenna

# Typical CR Lab Design Procedure

Prepare system requirements and constraints (frequency of operation, ADC sampling rate, etc.) Build the communication chain for transmitter and receiver on parallel (one block at a time) Test the communication chain under simulation environment -> understand the limitation of the design Add the UHD interfaces and test the design on the testbed

Debug, troubleshoot and iterate

# UHD USRP Source/Sink Block

ECE8863

## UHD: USRP Source - Used in receiving path

| Pr                       | operties: UHD: USRP Source | X  |          |

|--------------------------|----------------------------|----|----------|

| Parameters:              |                            |    |          |

| <u>ID</u><br>Output Type | uhd_usrp_source_0          | =  |          |

| Device Addr              | addr=192.168.20.2          |    |          |

| Ref Clock                | Internal 🗘                 |    |          |

| Sync                     | don't sync 🗘               |    |          |

| Clock Rate (Hz)          | Default 🗸                  |    |          |

| Num Mboards              | 1 ~                        |    |          |

| Mb0: Subdev Spec         |                            |    |          |

| Num Channels             | 1 ~                        |    |          |

| Samp Rate (Sps)          | samp_rate                  |    | NBX: fi> |

| Ch0: Center Freq (Hz)    | 900e6                      |    |          |

| Ch0: Gain (dB)           | 0                          |    | TX/RX B  |

| Ch0: Antenna             | RX2                        |    |          |

| Ch0: Bandwidth (Hz)      | 0                          |    | 3W must  |

|                          | Cancel                     | ок | set to O |

## UHD: USRP Sink

## - Used in transmitting path

|           | 🗖 📐 P                 | Properties: UHD: USRP Sink | × |

|-----------|-----------------------|----------------------------|---|

|           | ID                    | uhd_usrp_sink_0            |   |

|           | Input Type            | Complex   \$               |   |

|           | Device Addr           |                            |   |

|           | Ref Clock             | Internal 😂                 | - |

|           | Sync                  | don't sync 🛛 🗢             |   |

|           | Clock Rate (Hz)       | Default                    |   |

|           | Num Mboards           |                            |   |

|           | Mb0: Subdev Spec      |                            |   |

|           | Num Channels          |                            |   |

|           | Samp Rate (Sps)       | samp_rate                  |   |

|           | Ch0: Center Freq (Hz) | 900e6                      |   |

| BX: fixed | Ch0: Gain (dB)        | 0                          |   |

| X/RX BW   | Ch0: Antenna          | TX/RX                      |   |

|           | Ch0: Bandwidth (Hz)   | 0                          |   |

| N must be |                       |                            | ~ |

| t to 0 🗖  |                       | Cancel OK                  |   |

|           |                       |                            |   |